GDP-AI for Virtuoso

High-performance design & IP management for Cadence Virtuoso

GDP-AI offers comprehensive design & IP management for teams doing analog, RF, and mixed-signal IC design with Cadence Virtuoso.

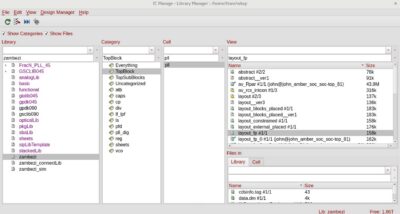

Engineers access GDP-AI directly from their Cadence Virtuoso design environment (Virtuoso ADE, Virtuoso Studio…), enabling version control, workspace management, and seamless navigation of libraries, cellviews, schematics, layouts, symbols, and simulation data without disrupting established workflows.

Built for complex custom IC structures, GDP-AI delivers fast navigation, clear visibility into design state, and integrated version control across related design objects — supporting consistent development processes across complex hierarchies and distributed teams.

Built for custom IC design

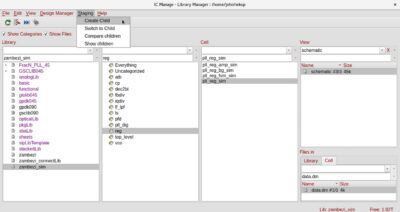

Custom IC design flows present unique challenges due to deeply hierarchical structures and tightly coupled schematic, layout, symbol, and simulation views. GDP-AI is built to address these complexities, enabling efficient interaction with complex hierarchical design structures.

IC Manage GDP-AI is tightly integrated with Cadence Virtuoso and extends the design management functionality well beyond the Virtuoso’s design management API. It provides significant advantages over other design management systems.

Its high-performance streaming C++ architecture delivers substantially faster operations across very large hierarchies, including libraries containing tens of thousands of cells — enabling rapid navigation and interaction with complex design structures along with their design management state. This improves responsiveness when working with large analog and mixed-signal libraries, especially across multi-site environments.

Key information is immediately visible at the top level, allowing users to quickly view critical data without navigating multiple layers of the hierarchy. Designers can tailor the look and feel to match their workflow preferences.

Workspace configuration & library population

Engineering teams configure workspaces through GDP-AI’s web-based GUI, defining named libraries and populating workspaces with design data — creating consistent, reusable workspace structures that team members can immediately use and replicate across projects and derivative designs.

It automates the library population process via configurable filtering that ensures only valid design data enters version control. When source libraries are imported, GDP-AI distinguishes design data from system-generated artifacts that should not be versioned using IC Manage’s built-in rules combined with user-defined logic.

The Cadence Virtuoso vendor data registry provides an additional layer of management aligned with Virtuoso conventions, automatically excluding system-generated files while designating recognized types, such as SPICE formats, as valid content.

Engineers can initialize libraries as empty structures and then populate them with validated source content, enabling consistent workspace configurations across teams. Once defined, these configurations can be reused to rapidly establish new workspaces or derivative projects — reducing manual setup effort while maintaining standardized structure and data integrity across complex design programs.

Revision visibility and design traceability

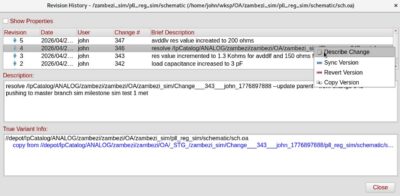

GDP-AI ensures design integrity through comprehensive visibility and full lifecycle traceability when designing in Virtuoso.

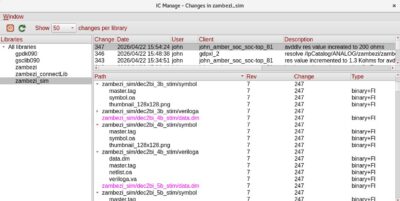

- Visual revision history. Access and review revision history at the library, cell, and view level using sortable change lists — quickly understanding how designs evolved and identifying when specific modifications were introduced.

- Revision control & snapshots. Engineers can revert to prior revisions when necessary, while using release snapshots to preserve stable design states required for tapeout.

- Audit & compliance. GDP-AI leverages full revision traceability to support audit and compliance requirements for regulated industries, including automotive and aerospace.

- Advanced IP management with integrated defect tracking. Team members can track IP development, usage, and defects across global enterprises, propagating fixes to every affected project, and giving IP owners, engineers, and executives complete visibility and control over every internal and third-party IP asset across ASIC, SoC, and FPGA programs,

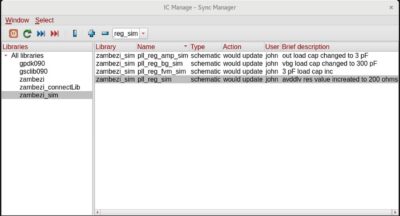

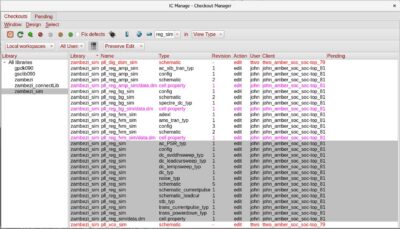

Sync management across teams

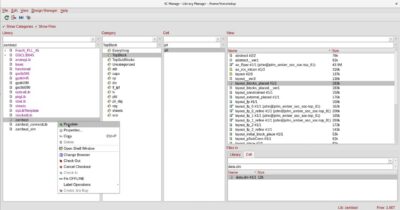

GDP-AI provides designers with a real-time global view of workspace alignment, clearly identifying which design objects are out of sync with the rest of the team.

When a schematic changes, engineers can immediately see its potential impact on layout, enabling schematic, layout, and verification teams to coordinate before committing changes.

Designers selectively sync the relevant design objects before performing a final atomic check-in to maintain consistency across schematic, layout, and related views while enabling parallel development within the same hierarchy.

The atomic check-ins capture all related design objects in a single, consistent transaction — preventing partial updates and eliminating any doubt as to whether or not all files were committed.

Staging: Advanced workflow for IP block development

The GDP-AI staging feature uniquely enables engineers to create private development branches while preserving exclusive checkouts across selected namespaces. Private branches contain private version history that is not exposed to the main line until pushed or pulled by designer. Because exclusive checkouts are preserved, engineers can safely replace objects without merging.

This feature enables highly parallelized workflows, similar to those used by software developers, overcoming the binary file merging problem that has traditionally forced custom IC designer to work in a single branch.

Staging workflows enable controlled push/pull/replacement of changes once development tasks are completed, maintaining consistency across complex hierarchical designs. When multiple versions of the same IP module are used within a single design, staging branches can be renamed to prevent namespace collisions without breaking revision lineage. Renamed branches are virtual projections rather than physical clones, so full lineage is maintained without duplicating underlying data.

GDP-AI: Custom IC design & IP management market leader

IC Manage GDP-AI is the defacto standard for design & IP management for custom IC design, dramatically enhancing efficiency for analog, RF, mixed-signal, standard cell, and memory IC development.

Customers include Altera, AMD, Apple, Infineon, Microchip, NVIDIA, Qualcomm, Samsung, Viasat, and dozens of other top semiconductor and systems companies.

Graphical design diff – Comparing design revisions

GDP-AI’s graphical design differencing allows engineers to visually compare schematic and layout revisions to identify changes across hierarchical design structures.

Designers can immediately identify differences in component parameters, connectivity, device properties, routing, and other structural elements, accelerating their analysis of the impact of design modifications.

![]()

Efficient, fast multi-site collaboration

GDP-AI scales from small analog teams to the enterprise level with thousands of engineers collaborating across global design centers. Automated workspace synchronization between main servers and regional cache servers ensures that designers in every location have high-speed access to the same single source of truth.

Smart metadata caching improves data access performance, and offline mode supports continued productivity when network connectivity is limited. Library sharing infrastructure reduces workspace population time from hours to seconds, dramatically reducing storage requirements through soft links to IP rather than physical file duplication.

![]()

AI-Driven Workflow Automation

GDP-AI embeds powerful AI-assisted workflow automation directly into the design data management workflow in Virtuoso, enabling engineers to navigate and manage complex analog, RF, mixed-signal design, standard cell, and memory design data faster and more intuitively through natural language queries, real-time design data access, and semantic documentation search.

AI-generated executable scripts automate routine data management tasks including workspace creation, branch management, and derivative configurations, while live project insights and precise technical responses accelerate decision-making and shorten the path to error-free tapeout.

![]()

Unified Environment for Heterogeneous Design Assets

GDP-AI provides a unified environment for managing heterogeneous design assets in Virtuoso, supporting consistent version control and release processes across analog and digital domains.

Custom IC development often requires coordination across multiple design data types, including OpenAccess libraries, simulation scripts, documentation, digital design sources, firmware, and software. With GDP-AI, all are managed within a single, coherent system.

Support for OpenAccess and CDBA database formats ensures alignment with established custom IC design flows. IC Manage GDP-AI’s integration with Git and Perforce repositories allows organizations to leverage existing infrastructure within collaborative design workflows.

Key Takeaways: GDP-AI for Virtuoso Custom IC Design

This section summarizes how GDP-AI, the de facto standard for Virtuoso design & IP management, solves complex hierarchical versioning and synchronization challenges for analog, RF, mixed-signal, standard cell, and memory design teams worldwide — with high-performance C++ architecture and AI-driven workflow automation.

- Product. GDP-AI is the de facto standard for custom IC design & IP management in Virtuoso — delivering high-performance, integrated design data management in Cadence Virtuoso, enabling analog, RF, mixed-signal, standard cell, and memory design teams, from small groups to thousands of engineers across global enterprises, to perform version control, workspace management, hierarchical library navigation, and full revision traceability.

- Key Challenge. Custom IC designs’ deeply hierarchical structures with tightly coupled schematic, layout, symbol, and simulation views create version control risks, slow navigation across large libraries, and can cause broken lineage in IP derivatives and synchronization gaps that conventional library-browser-based design management cannot resolve at scale; IC Manage addresses through atomic check-ins, real-time sync visibility, and revision traceability to reduce integration risk and de-risk tapeout.

- Competitive Advantages. GDP-AI delivers capabilities unavailable in competing systems limited to browser extensions: a high-performance C++ architecture delivering substantially faster navigation across very large libraries; advanced staging that creates private IP block branches without namespace collisions; clear top-level visibility of design state; configurable workspace filtering with vendor-aware rules that automatically separate valid design data from system-generated artifacts; advanced IP management; and AI-driven workflow automation generated directly from natural language prompts.

- Design Flow Fit. IC Manage’s high-performance GDP-AI is integrated into analog, RF, mixed-signal, standard cell, and memory design flows, supporting the complete front-end and back-end lifecycle — from initial library and workspace configuration through IP block development, parallel schematic and layout co-design, simulation data management, and tapeout release.

- Engineering Benefits. GDP-AI reduces workspace setup overhead through reusable configurations that cut workspace population time from hours to seconds, accelerates coordination through real-time sync visibility, enables safe parallel IP development through staging branches that eliminate namespace collisions, and delivers more predictable tapeout readiness — trusted by NVIDIA, Qualcomm, AMD, Samsung, Infineon, Microchip, Apple, Viasat, and dozens of other leading semiconductor and systems companies for their custom IC designs.

- Ecosystem. GDP-AI is tightly integrated with Cadence Virtuoso design environments such as Virtuoso ADE and Virtuoso Studio, supports OpenAccess and CDBA database formats, connects with Git and Perforce repositories, and plugs into GDP-AI’s broader platform capabilities — including staging, advanced branching, audit and compliance support, and defect tracking — with automated proxy cache synchronization delivering high-speed design data access across distributed global teams.

What is Virtuoso Design Management?

Virtuoso design management (also known as Virtuoso design data management) provides high-performance version control and workspace management integrated directly into Cadence Virtuoso to handle the complex hierarchical structures of analog, RF, and mixed-signal designs.